基于高分辨率CMOS传感器图像采集系统的实现

随着CMOS技术的发展,原来CMOS图像传感器比CCD噪声大的特点得到大大改善,并且以其成本低、功耗低、单一工作电压、集成AD转换器、数字形式数据输出、图像大小可编程控制等优点,在摄像头、微型数码照相机、扫描仪、手机、可视电话、视频会议等众多领域应用。但要将CMOS的图像采集到DSP芯片中的硬件设计成本较高,实现难度较大。现阶段,比较多的方案是采用带视频控制器的DSP芯片,如TI6000系列中带有3个VPO接口的TMS320DM642和ADI公司带PPI接口的Blackfin处理器。很多低价通用的DSP如TI55x系列和67x系列的DSP,与CMOS图像传感器都没有直接接口,需要设计硬件电路。本文便是针对这种低价通用的DSP,提出的一种低成本的采集方案。

1 系统设计

由于大部分DSP都有与SDRAM、Flash、SRAM、FIFO等存储器接口的EMIF接口,而没有直接与CMOS/CCD固体图像传感器接口的控制器。所以采用CPLD作为图像传感器到FIFO以及FIFO到DSP的一个时序协调控制器。同时由于图像传感器的像素时钟PIXCLK很高,最高可以达到48MHz,固体图像传感器的图像数据量大,而FIFO的容量有限,一般都是几K、几十K字节,对于高像素的图像来说,FIFO只能充当线缓冲的作用,要作为帧缓冲,除非系统对速度要求很高,否则成本太高。由于采集到DSP中的图像数据量很大,靠写文件的方式来验证采集的数据非常慢,所以本系统采用GPIO设计了一个SD卡的控制器,通过写BMP文件,对采集的图像进行验证。系统设计框图如图1所示。

本系统设计的关键在于DSP采用何种方式去读取FIFO中的图像数据。很多方案中都是启动EDMA读取FIFO中的图像数据,当FIFO半满时中断DSP启动EDMA读取数据,这样对FIFO读时钟的频率要求很高,需要读时钟为写时钟的2倍。但这种方案存在问题,即FIFO时钟的选择问题。EMIF口的 在EDMA启动的过程中都是一些不稳定不规则的负脉冲信号,难以选择作为FIFO的读时钟。这种采用EDMA的方案在TMS320DM642中可行,因为TMS320DM642能与FIFO无缝连接。

在EDMA启动的过程中都是一些不稳定不规则的负脉冲信号,难以选择作为FIFO的读时钟。这种采用EDMA的方案在TMS320DM642中可行,因为TMS320DM642能与FIFO无缝连接。

2 硬件设计

2.1 硬件电路图

本系统硬件连接如图2所示,所采用的图像传感器型号是MT9T001,它是一款主要针对数码相机领域的CMOS图像传感器。与其他的CMOS图像传感器相比,MT9T001有以下明显的特点:

(1)像素大小可以通过IIC接口改变相应寄存器进行硬件裁剪。

(2)高的帧速,输出为QXGA分辨率(2 048×1 536)时,可以达到12f/s,而输出为VGA分辨率(320×240)时,有93f/s。

(3)高性能的低照度成像性能。

(4)具有AF对焦窗口的图像输出格式,如图3所示,(2 048×512)时,可以达到30f/s。

硬件设计主要体现在CPLD的逻辑上面。本系统采用ALTERA公司的CPLD芯片EPM240作为系统的逻辑控制器件,有80个I/O引脚和240个逻辑单元,资源足够满足各种方式的采集设计的需要。

DSP采用TI公司的TMS320C6711DSK板,TMS320C6711DSK有以下特点:

(1)板上留有2个80脚的接口,方便系统扩展;

(2)EMIF接口有两种时钟模式可以选择,时钟频率分别为150MHz和100MHz;

(3)100MHz的16MB同步动态存储器(SDRAM);

(4)直接提供1.8V和3.3V直流电源;

(5)JTAG仿真器,可支持并口或外接XDS510支持;

(6)1个并行接口,主机可通过该并口访问开发板上的存储器;

(7)150MHz主频,可执行900 MFLOPS浮点操作;

(8)128KB的可编程Flash存储器;

(9)16位语音CODEC电路。

2.2 CPLD内部的逻辑

TMS320C6711的EMIF口连接异步存储器的时序如图4所示。

从时序图可以看出, 在 的上升沿便读取一次数据,所以用这个引脚来作为读取FIFO的时钟最合适。如果用ECLKOUT读取,需要在CPLD中设计计数器,很不方便,也不灵活。图5为CPLD内部逻辑图。

的上升沿便读取一次数据,所以用这个引脚来作为读取FIFO的时钟最合适。如果用ECLKOUT读取,需要在CPLD中设计计数器,很不方便,也不灵活。图5为CPLD内部逻辑图。

图5 逻辑连接图

3 软件设计

3.1 图像传感器的配置

SCLK和SDATA两条线构成了该串行总线,SCLK为串行时钟,SDATA为串行数据。两条线通过1.5kΩ的电阻上拉到3.3V。在实际应用中,通过上拉1.3kΩ电阻,用TMS320VC6711(外扩一片EPM240实现)模拟总线时序,完全可以达到要求。其操作方法几乎和IIC总线一样,在速度和位数上稍微有一点差别,限于篇幅不再赘述。图6为写时序图,图7为读时序图。

芯片内部集成了模拟处理电路(10bit A/D转换器,放大器)、时钟控制电路(反相,相位调节)、图像大小调节、原点定位、白平衡调节、曝光调节、帧速率调节等众多功能电路,所有这些控制都通过一个串行总线口进行操作(SCLK和SDATA)。数据输出则为10bit并行口,数据同步时钟PIXCLK,行同步LINE_VALID和帧同步信号FRAME_VALID。

在本系统设计中,由于在绿色通道增益最低的情况下采集到的图像还是偏绿,所以对红色和蓝色通道的增益调大了少许。

3.2 系统的主体程序

视频采集系统软件需要完成CMOS图像传感器图像数据的采集、转换和图像数据的存储功能。

为了便于后期图像处理和分析工作,采用了DSP BIOS的程序设计架构。BIOS上的程序总体设计流程图如图8所示。

中断触发源采用了EXT4,即外部中断引脚中断。而外部引脚连接的是行有效信号,这样,每一行便触发一次中断,然后在中断服务程序中通过读取FIFO的数据到SDRAM中,完成一行数据的采集,通过行计数器来判断一帧是否传完。值得注意的是,本系统的软件设计没有采用两级中断来保证第一行读到的图像数据就是图像本身的第一行,而是采用读取行同步信号的上升沿来简化程序。

由于在TI公司的CCS3.1开发环境下面写文件方式的速度太慢,所以采用DSP写SD卡的方法来保存图像数据,采集到更加清晰的图像,如图9。

MT9T001图像传感器的灵敏度很高,在很低的照度下都能清晰成像。要调整好镜头的光圈以避免出现局部过曝光的现象。

虽然采用DSP的EMIF接口外加FIFO行缓冲器的方案没有那些有专门视频接口的DSP(如DM642)的VP0-VP3端口方便,但本方案具有成本上的优势;同时在浮点运算特别多的图像算法中,本方案的算法效率要比DM642高。本方案对很多没有视频控制器的DSP具有通用性;另外,本方案扩展了一片CPLD,可以对硬件控制进行一些灵活的处理,如可以通过对HD信号灵活计数,控制闪光灯的点亮时间等。

实验证明,本系统适合带有EMIF接口的DSP系统,这种图像采集接口还能很好地移植到其他基于DSP的图像采集与处理系统中。

提交

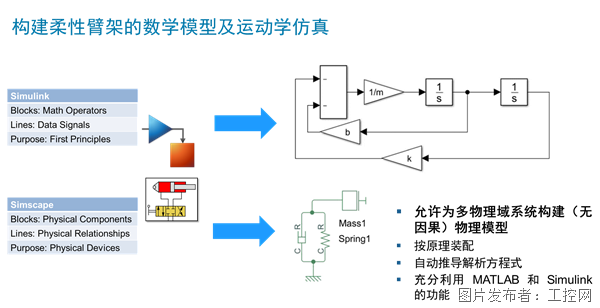

超越传统直觉,MATLAB/Simulink助力重型机械的智能化转型

新大陆自动识别精彩亮相2024华南国际工业博览会

派拓网络被Forrester评为XDR领域领导者

智能工控,存储强基 | 海康威视带来精彩主题演讲

展会|Lubeworks路博流体供料系统精彩亮相AMTS展会

投诉建议

投诉建议